模拟集成电路设计课程设计

根据运算放大器设计要求(单位增益带宽、 相位裕量、 功耗等),分析 CMOS运算放大器的所有性能指标。使用 Level one 模型进行手工计算,设计出所有器件的尺寸参数,然后,通过 Tspice软件仿真验证,给出所有性能指标的仿真结果。

一、要求:

1、开环直流增益 ≥ 80 dB

2、单位增益带宽 ≥ 100KHz

3、相位裕量 ≥ 50 degree

4、负载电容 = 2 pF

5、摆幅 [0.25*(VDD-VSS), 0.75*(VDD-VSS)]

6、电源电压 5V

二、原理分析

原理图:

实验原理:

电路选用二级米勒补偿,其中一级放大主要是放大增益,二级是放大摆幅,将电路分三部分来看

左边:用直流电压为m1,m2提供偏置电压

中间:m3,m4,m5,m6,m1一路选用差分放大电路作为一级放大

右边:m2,m7一路是提高输出摆幅电路部分

Cc为补偿电容,而电感L起稳压作用

为达到设计指标,对运算放大器的每个moS管都要在饱和区工作,通过对原理图的小信号分析得到这种结构的增益为Gain = gm1×gm6/(gds2 + gds4)/(gds6 + gds7)表示,其中gds2 , gds4, gds6 , gds7,分别为M2,M4,M6,M7管的相关电导。gm1,gm6分别M1、M6的跨导。而输出电压摆幅为Vincm.max=Vdd-|VGS3|+Vthn,Vincm.min=Vod5-VGS1=Vod5+Vod1+Vthn1,其中Vod1、Vod5分别为M1和M5的过驱动电压。

三、设计步骤:

1. 由已知的CL并根据转换速率的要求(或功耗要求)选择ISS(I9)的范围;

2. 计算满足频率要求的Rout范围,否则,改变ISS;

3. 设计W3/L3( W4/L4)、W5/L5( W6/L6)满足上ICMR(或输出摆幅)要求;

4. 设计W2/L2、 W7/L7满足增益要求;满足下ICMR(或输出摆幅)要求;

5. 若达不到设计要求,重复上述过程。

四、运放电路的参数以及仿真结果:

1初步仿真、

初始参数:

C1 N2 OUT 10pF

C2 OUT Gnd 2pF

L1 OUT N3 100000000000000Gu

M7 OUT N2 Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M5 Gnd N5 N5 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M6 N2 N5 Gnd Gnd NMOS L=2u W=22u AD=66p PD=2u AS=66p PS=24u

M1 N7 N4 Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M2 OUT N4 Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M3 N5 N3 N7 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M4 N7 N6 N2 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

v4 N6 N3 -0.0007 AC 1.0 0

v1 Vdd Gnd 5.0

v3 N4 Gnd 4.0

结果:

上表中的相位裕度,开环直流增益并不符合设计要求,其它指标几乎满足要求。

原因是我们在手算时只是为设计提供一个参考,所以在推导过程中又进行了许多近似处理以简化公示,减小运算量,这又使手算结果后天不准确。所以在根据手算结果设计好电路后,还要针对指标的偏差进行必要的调整。

2、调整及结果:

为了提高增益,可增大M3、M4,M6的W/L比。这里的相位裕度还不满足,为了达到要求改变M5,M1,M2,M6的W/L比。一边仿真一边修改,增大M6、M8的W/L比,增大ROUT,提高主极点降低GX,通过调节M5,M1,M2,M6的W/L比,提高PX。最后调节得到的参数为:

Cc N1 OUT 10pF

Cl OUT Gnd 2pF

L1 OUT N3 100000000000000Gu

M7 OUT N1 Gnd Gnd NMOS L=2u W=160u AD=66p PD=24u AS=66p PS=24u

M5 Gnd N5 N5 Gnd NMOS L=2u W=2u AD=66p PD=24u AS=66p PS=24u

M6 N1 N5 Gnd Gnd NMOS L=2u W=2u AD=66p PD=2u AS=66p PS=24u

M1 N7 N4 Vdd Vdd PMOS L=2u W=2u AD=66p PD=24u AS=66p PS=24u

M2 OUT N4 Vdd Vdd PMOS L=2u W=2u AD=66p PD=24u AS=66p PS=24u

M3 N5 N3 N7 Vdd PMOS L=2u W=120u AD=66p PD=24u AS=66p PS=24u

M4 N7 N6 N1 Vdd PMOS L=2u W=120u AD=66p PD=24u AS=66p PS=24u

v4 N6 N3 -0.0007 AC 1.0 0

v1 Vdd Gnd 5.0

v3 N4 Gnd 4.0

结果:

下面是从Tspice仿真后得到的list文件中得到的每一个晶体管的工作点:

AC SMALL-SIGNAL MODELS

0 1 2 3 4

M1 M2 M3 M4 M5

MODEL pmos pmos pmos pmos nmos

TYPE PMOS PMOS PMOS PMOS NMOS

ID -1.73e-006 -1.82e-006 -8.58e-007 8.72e-007 -8.58e-007

VGS -1.00e+000 -1.00e+000 -1.04e+000 1.14e+000 0.00e+000

VDS -1.96e+000 -3.00e+000 -2.27e+000 2.18e+000 -7.74e-001

VBS 0.00e+000 0.00e+000 1.96e+000 4.14e+000 -7.74e-001

VTH -6.45e-001 -6.43e-001 -1.11e+000 -1.11e+000 7.39e-001

VDSAT 2.79e-001 2.81e-001 2.92e-002 2.92e-002 1.30e-001

RS 0.00e+000 0.00e+000 0.00e+000 0.00e+000 0.00e+000

RD 0.00e+000 0.00e+000 0.00e+000 0.00e+000 0.00e+000

GM 8.98e-006 9.38e-006 3.14e-005 -3.12e-005 -9.87e-006

GDS 8.96e-008 7.59e-008 9.46e-008 3.83e-005 1.00e-005

GMB 1.91e-006 1.99e-006 6.90e-006 -7.00e-006 0.00e+000

GBD 1.01e-012 1.01e-012 1.01e-012 1.01e-012 1.01e-012

GBS 1.01e-012 1.01e-012 1.01e-012 1.01e-012 1.01e-012

CGS 4.70e-015 4.70e-015 8.35e-014 4.02e-014 5.78e-016

CGD 6.70e-016 6.70e-016 4.02e-014 8.37e-014 5.42e-015

CGB 5.15e-016 5.15e-016 4.61e-014 4.58e-014 0.00e+000

CBD 2.45e-014 2.13e-014 1.98e-014 2.11e-014 2.43e-014

CBS 3.76e-014 3.76e-014 2.10e-014 1.98e-014 1.41e-014

5 6

M6 M7

MODEL nmos nmos

TYPE NMOS NMOS

ID 8.72e-007 1.68e-004

VGS 7.74e-001 8.63e-001

VDS 8.63e-001 2.00e+000

VBS 0.00e+000 0.00e+000

VTH 7.38e-001 7.28e-001

VDSAT 1.31e-001 1.99e-001

RS 0.00e+000 0.00e+000

RD 0.00e+000 0.00e+000

GM 9.97e-006 1.22e-003

GDS 1.50e-007 1.48e-005

GMB 0.00e+000 0.00e+000

GBD 1.01e-012 1.01e-012

GBS 1.01e-012 1.01e-012

CGS 5.42e-015 4.31e-013

CGD 5.78e-016 4.62e-014

CGB 0.00e+000 0.00e+000

CBD 9.81e-015 8.50e-015

CBS 2.43e-014 -3.65e-014

四、附录

1、直流分析:(DC ANALYSIS)

v(N7) = 3.0417e+000

v(OUT) = 2.0000e+000

v(N2) = 8.6261e-001

v(N5) = 7.7356e-001

v(N3) = 2.0000e+000

v(N4) = 4.0000e+000

v(Vdd) = 5.0000e+000

v(N6) = 1.9993e+000

i(v4) = 0.0000e+000

i(v1) = -3.5455e-006

i(v3) = 0.0000e+000

i(v2) = -1.6624e-004

2、下图为交流分析图像

七、实验结论:

七、实验结论:

运算放大器在模拟集成电路和混合数字信号系统中有着广泛的应用,因而设计高性能的运算放大器可以使系统的总体性能得到提高。本文设计一种单级高增益运算放大器,电路结构选定为共源共栅运算放大器通过对电路的一些参数的设置以达到高增益的目的,通过tanner软件T-SPICE仿真,得出可接近实验要求的运算放大器。

本设计采用折叠式级连共源共栅运算放大器具有高增益、高输出摆幅和频率特性好等特点。通过对运算放大结构的小信号分析得到这种结构的放大倍数

Av=gm3*Rout=gm3(ro2//ro7) ,其中ro2,ro7分别为M2,M7的输出阻抗,增益为Gain = gm1×gm6/(gds2 + gds4)/(gds6 + gds7)表示,其中gds2 , gds4, gds6 , gds7,分别为M2,M4,M6,M7管的相关电导。gm1,gm6分别M1、M6的跨导。而输出电压摆幅为Vincm.max=Vdd-|VGS3|+Vthn,Vincm.min=Vod5-VGS1=Vod5+Vod1+Vthn1,其中Vod1、Vod5分别为M1和M5的过驱动电压。

本文设计的折叠式级连共源共栅运算放大器充分应用到了电路的高增益特点,而且同时保证每个mos管都达到了饱和。本文中设计的运算放大器采用了共模反馈,折叠式的级连方式,使系统达到更稳定,更大的放大倍数,更大的增益和输出摆幅。但是本放大器也有不足之处在于电压增益与M2,M7以及补偿电容,输出阻抗有关。

总之,全差动的折叠式级连共源共栅运算放大器相对于二级弥勒补偿等其他电路结构有更高的输出摆幅等的特点。

第二篇:电子实验报告二 集成运算放大器的基本应用

电路实验报告二

《集成运算放大器的基本应用》

实验内容:

A.反相比例运算电路

1、关闭系统电源。按图1-1正确连线。连接信号源的输出和Ui。

2、打开直流开关。调节信号源输出f=100Hz,Ui=0.5V(峰峰值)的正弦交流信号,用毫伏表测量Ui、UO值,并用示波器观察UO和Ui的相位关系,记入表1-1。

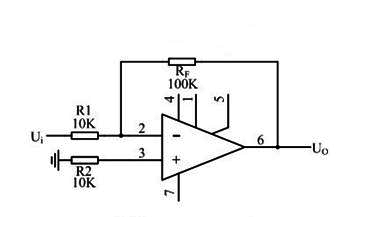

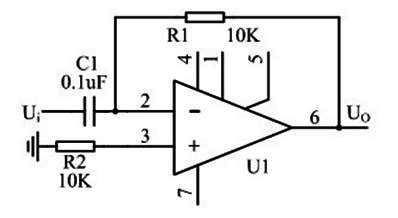

法相比例运算电路如下图1-1:

图1-1

表2-1

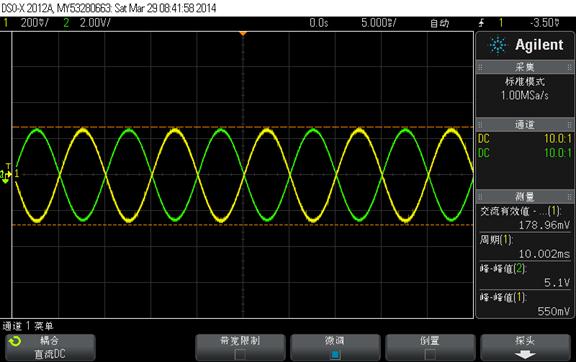

UO和Ui的波形图见图1-2,可知运算放大器的输出波形与输入波形反相。

图1-2

B.反相加法运算电路

1、关闭系统电源。按图2-1正确连接实验电路。连接直流信号源和Ui1、Ui2,

2、打开系统电源,用万用表测量输入电压Ui1、Ui2(且要求均大于零小于0.5V)及输出电压UO,记入下 表2-1。

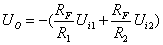

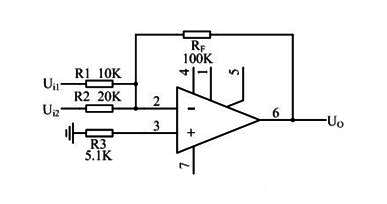

反相加法运算电路如下图2-1:(R1改为1k?, Rf改为10k?)

图2-1

表2-1

C.减法运算电路

1、关闭系统电源。按图3-1正确连接实验电路。采用直流输入信号。

2、打开系统电源。实验步骤同内容3,记入表3-1。

减法运算电路如下图3-1:

图3-1

表3-1

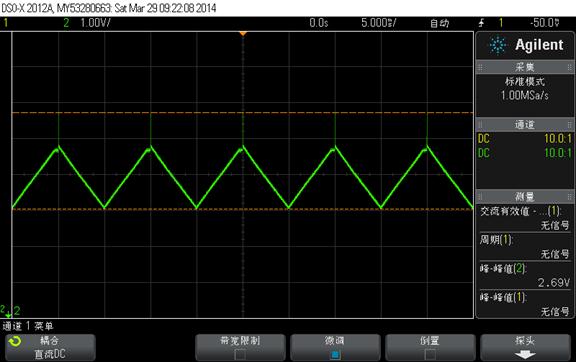

D.积分运算电路

1、关闭系统电源。按积分电路如图4-1所示正确连接。连接信号源输出和Ui。

2、打开系统电源。调节信号源输出率约为100Hz,峰峰值为2V的方波作为输入信号Ui,打开直流开关,输出端接示波器,可观察到三角波波形输出并记录之。

积分运算电路如图4-1:

图4-1

观察到的输出波形见图4-2:

图4-2

E.微分运算电路

1、关闭系统电源。按微分电路如图5-1所示正确连接。连接信号源输出和Ui。

2、打开系统电源。调节信号源输出率约为100Hz,峰峰值为2V的方波作为输入信号Ui,打开直流开关,输出端接示波器,可观察到尖顶波波形输出并记录之。

微分运算电路如图5-1:

图5-1

观察到的输出波形见图5-2:

图5-2