四川大学网络教育学院

实践课程报告

实践课程:电工电子综合实践

校外学习中心:陕西神木奥鹏学习中心

专业:电气工程及自动化

层次:高起本

年级:07秋

学生姓名:刘永平

学号:BH1072h1005

20##年2月16日

实验项目名称:数据选择器的应用

一、 实验目的和要求:

1) 实验目的

A. 通过实验的方法学习数据选择器的电路结构和特点。

B. 掌握数据选择器的逻辑功能及其基本运用。

C. 学会利用数据选择器的逻辑功能去进行一些复杂的逻辑运算。

2) 实验要求

3) 按实验要求认真操作实验步骤中的每一条。

4) 做完实验后给出本实验的实验报告。

二、 实验设备

1) 数字电路实验箱

2) 74LS153 74LS00 74LS86

三、 实验原理

数据选择器(multiplexer )又称为多路开关,事一种重要的组合逻辑部件,它可以实现从多路数据中选择任何一路数据输出,选择的控制由专门的端口编码决定,称为地址码,数据选择器可以完成很多逻辑功能,例如函数发生器、桶形移位器、并串转化器、波形产生器等。

1. 双四选一数据选择器

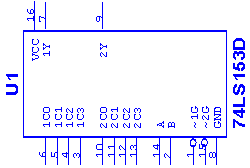

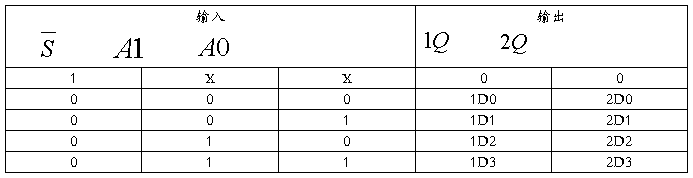

常见的双四选一数据选择器为TTL双极型数字集成逻辑电路74LS153,它有两个四选一,外形为双列直插,示,逻辑符号如图3.1。其中 为数据输入端,

为数据输入端, 为数据输出端,

为数据输出端, 为数据选择器的控制端(地址码),同时控制两个选择器的数据输出,

为数据选择器的控制端(地址码),同时控制两个选择器的数据输出, 为工作状态控制端(使能端),74LS153的功能参见表4.1

为工作状态控制端(使能端),74LS153的功能参见表4.1

图3.1

2. 用四选一数据选择器74LS153实现全加器

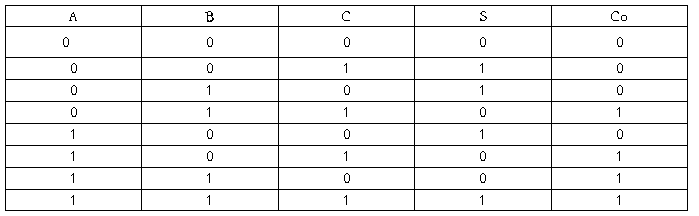

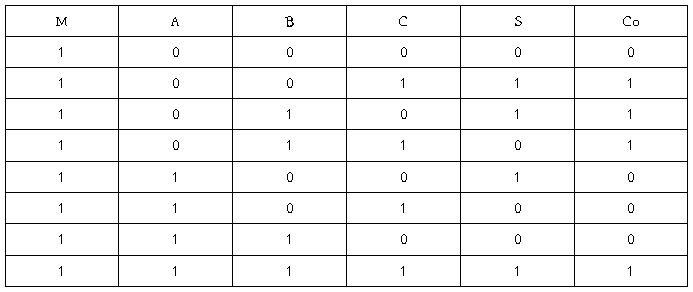

由题目要求可知,要实现的加法器是以二进制作运算的,其真值表如图4.1所示:其中A,B表示参加加法运算的项,C为来自低位的进位,则S为所加数的和,Co为向高位的进位,则ABC的逻辑关系进行转化可得出以下的逻辑关系表4.1:

全加器真值表

表4.1

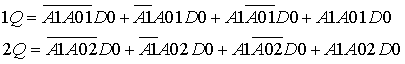

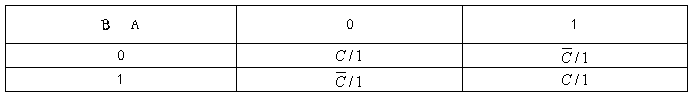

所以:对应于四选一数据选择器,用全加器的输入端A,B代替数据选择器的控制端,用来自低位的进位C的不同状态来代替数据选择器的输入端,则输出1Q,2Q就是所得的结果:S和Co。且输入与输出的关系式为:

3. 用四选一数据选择器实现全加全减电路。

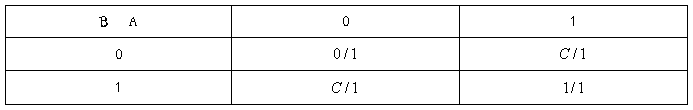

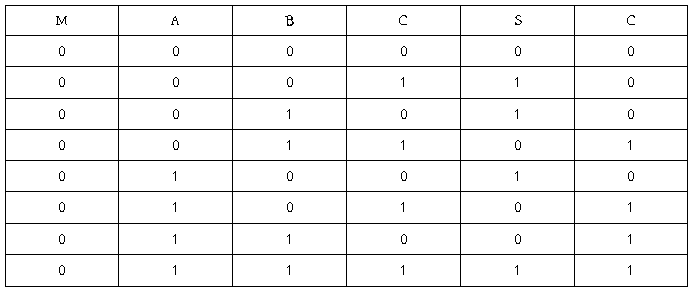

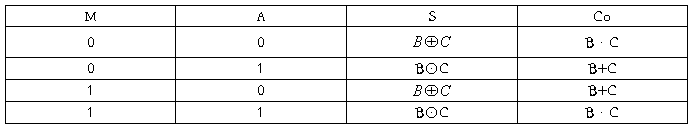

按照题目要求,实现全加全减为一体的电路只需要用一个输入量M加以区分即可,当M=1时电路为全减器,当M=0时电路为全加器。此时逻辑电路的真值表可表示为:

全加全减器真值表

表5.1

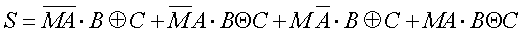

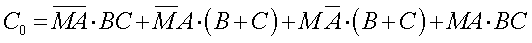

由上表观察可知,对应于四选一数据选择器,用输入端A,M代替数据选择器的控制端,用来自低位的进位C和B用门电路实现的不同状态来代替数据选择器的输入端,则输出1Q,2Q就是所得的结果:S和Co。且输入与输出的关系式及这些变量之间的逻辑关系表为:

表6.1

且:

4. 74LS86电路与74LS00。

74LS86电路与74LS00的电路外形结构极为相似,但实现的逻辑功能是双变量的异或,而74LS00实现的双变量的与非。

四、 实验内容

1. 设计实现全加器,要求只能使用74LS153 74LS00门电路。

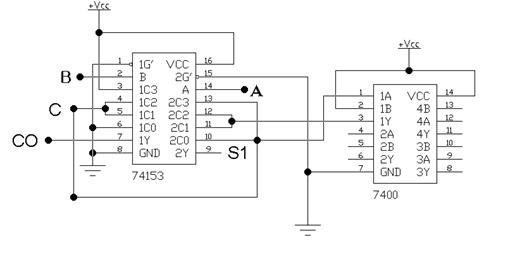

按实验原理中的内容依次在74LS153输入端接入相应的A,B,C信号即可。且三者之间的逻辑关系可以用74LS00来实现,连接电路的模拟图如下:

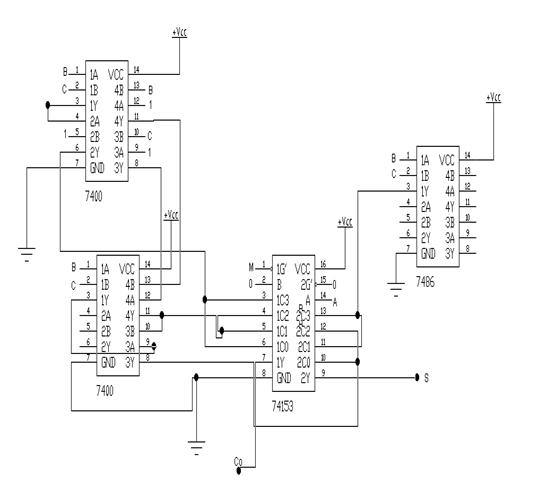

2. 设计实现全加全减的组合逻辑电路,要求当M=1时电路为全减器,当M=0时电路为全加器,电路由74LS153,74LS00,74LS86组合。

按照实验内容一的步骤及实验原理3,电路的连接如下图所示:

五、 实验结果分析

通过开关的闭、合来代表数据选择器的输入信号,通过两个灯

来表示输出结果,则显示的结果与真值表的内容一致。

六、 注意事项

1. 实验中因注意使能端接入低频信号,数据选择器才能正常工作。

2. M,A作为输入控制端时,顺序不能调换。

七、 实验心得

在本实验中,实现实验内容的方法很多,例如写出真值表的逻辑函数式,对照74LS153电路输出函数式,利用其他门电路拼凑出所需要的输入信号形式。同时降维配合观察真值表也是解决此类问题的捷径。

第二篇::数据选择器设计(实验报告)

实验报告

一、实验目的

熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验设备

GW48系列SOPC/EDA实验开发系统实验箱 一台 计算机 一台

三、实验内容

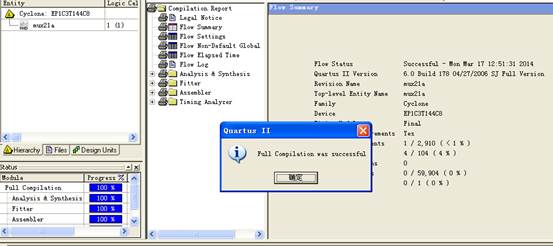

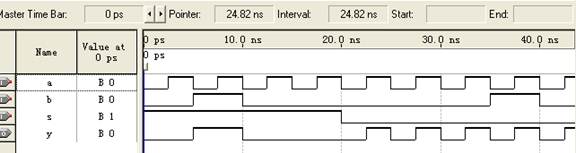

1首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出下图所示的仿真波形。最后在实验系统上进行硬件测试,验证本项设计的功能。

源程序为:

ENTITY mux21a IS

PORT ( a, b, s: IN BIT;

y : OUT BIT );

END ENTITY mux21a;

ARCHITECTURE one OF mux21a IS

BEGIN

PROCESS (a,b,s)

BEGIN

IF s = '0' THEN y <= a ; ELSE y <= b ;

END IF;

END PROCESS;

END ARCHITECTURE one ;

图(1 ) 2选1多路选择器的编译图

、 图(2) 功能仿真的波形图

图(3 ) 功能引脚图

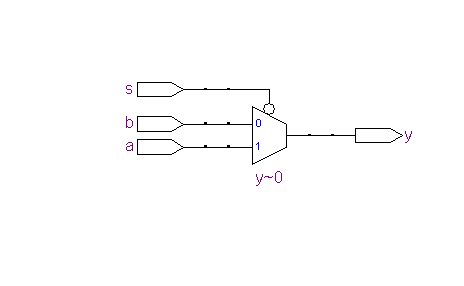

图(4) 2选1多路选择器的RTL电路

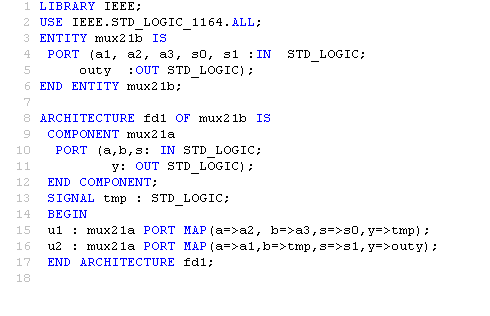

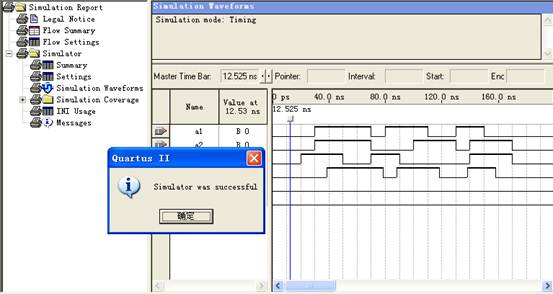

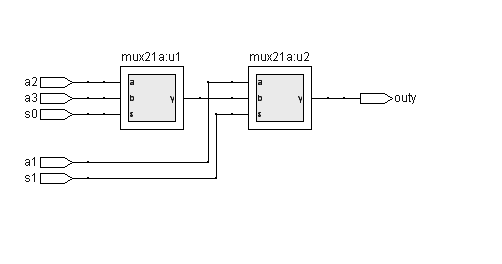

2. 将此多路选择器看成是一个元件mux21a,利用元件例化语句描述图,并将此文件放在同一目录中。并对上例分别进行编译、综合、仿真,并对其仿真波形做出分析说明。以下是程序:

图(5) 双二选一多路选择器的编译图

图(6) 双路数据选择器功能仿真图

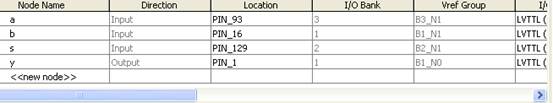

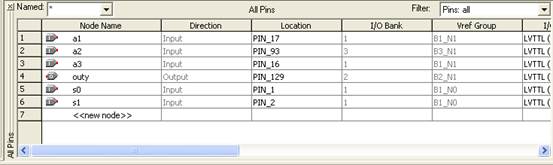

图(7) 双二选一多路选择器的引脚锁定图

图(7) 双二选一多路选择器的引脚锁定图

图 5 双2选1多路选择器

图(8) 双路数据选择器RTL电路图

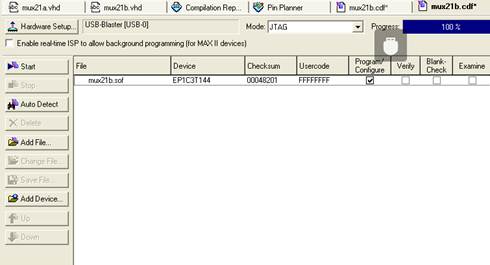

图(9) 编程下载图

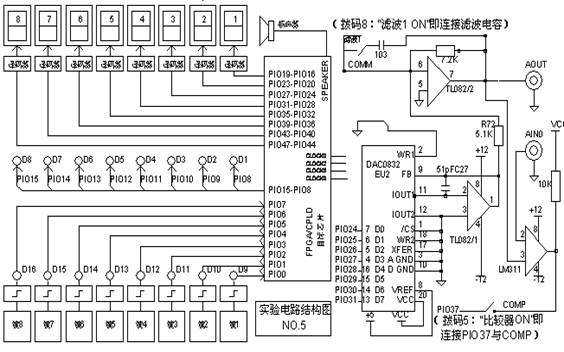

3.、引脚锁定以及硬件下载测试。若选择目标器件是EP1C3,建议选实验电路模式5,用键1(PIO0,引脚号为 1)控制 s0;用键 2(PIO1,引脚号为 2)控制 s1;a3、a2 和 a1 分别接 clock5(引脚号为 16)、clock0(引脚号为93)和clock2(引脚号为17);输出信号outy仍接扬声器spker(引脚号为129)。通过短路帽选择clock0接256Hz信号,clock5 接1024Hz,clock2 接8Hz 信号。最后进行编译、下载和硬件测试实验(通过选择键1、键2,控制s0、s1,可使扬声器输出不同音调)。

图(10) 实验电路模式5

图(11) 功能引脚图

四、实验总结

1实验存在的问题

上学期尽管学过quartusII但是由于长时间没有操作,很多都已经忘了,所以操作起来 不是很熟练。特别是程序下载方面。

2解决问题的方法

通过在实验中慢慢回忆起以前学的知识,渐渐熟悉其过程。再有问题就和同学交流帮忙!

3实验收获

对quartusII的操作方法更熟练了,也明白它是干什么的了!对软件有了更深的认识。同时也明白了!不管哪方面的学习都要温故而知新。